首页>技术中心>技术资讯>可编程逻辑器件在超声波流量计中的应用

可编程逻辑器件在超声波流量计中的应用

发布时间:2017-09-01

1引言

硬件描述语言HDL的出现使得数字系统的硬件构成及其行为完全可以用HDL语言来描述和仿真。这样,不熟悉硬件电路设计的人员同样可以借助HDL语言,设计出符合要求的硬件系统。不仅如此,利用HDL语言来设计系统硬件与传统的设计方法相比,还有许多突出的优点。HDL技术的引入必将是数字系统设计领域的一次革命。最早的可编程逻辑器件是采用TTL工艺生产的一次性可编程的PLA、PAL器件,它们只能实现一些简单的逻辑功能。随着可编程技术的不断发展,可编程器件的集成度和性能都有了很大的提高。

Altera公司最新推出的ACEX 1K PLD系列最多可含257 000个系统门,工作速度在115 MHz以上,可以完成一定的存储功能和各种复杂的逻辑功能,包括DSP纠错、宽带数据处理、微处理器应用以及数据传输等功能。设计采用的ispLSI 1032 80LJ84芯片,工作速度为80 MHz,有84个引脚,其中I/O引脚64个,内部包含有6000个PLD门,固定传输延迟是4.5ns,可重复编程10 000次以上;此外,ispLSI为在系统可编程器件,可不用编程器而直接在已设计好的目标系统或线路板上进行编程,想改变设计也十分方便。

2VHDL与开发软件Workview Office

大多数ASIC研制和生产厂家都开发了用于自己目的硬件描述语言,其中最有影响力的当属美国国防部开发的VHDL(Very High Speed Integrated CircuitHDL)和Verilog公司开发的Verilog HDL,两者都已被确定为IEEE国际标准。设计中使用的是VHDL语言,开发软件是Lattice公司提供的isp-VHDL View-logic系统。isp-VHDL是进行电子系统设计的强有力工具,它的使用可以大大提高设计的效率和产品的性能。这套软件由Viewlogic Workview Office和is-pDS+综合―优化逻辑软件两部分组成,具有强大的VHDL综合、原理图输入、功能与时序仿真、ispDS+适配器和isp-DOWNLOAD(菊花链下载)能力。

3系统硬件电路的集成化设计

超声波流量计硬件电路的结构十分复杂,所需分立件的数量较大,这给系统的设计和调试带来了很大的难度。将硬件电路中完成数字功能的大部分器件都集成到ispLSI 1032器件中去,大大降低了系统硬件的设计难度。

3・1计数器部分的集成化设计

计数电路的精度和稳定性对超声波流量计的整体性能至关重要。共使用8个计数器,4个用于计时电路,4个用于分频电路。其中,两个主计数器的长度为21位,编程有各自的片选、时钟输入、读信号、输出位数选择、计数使能和数据输出等端口。输出位数选择信号的作用是提高ispLSI器件I/O引脚的利用率,21位的计数值分3次由同一个8位数据端口输出,计数值的0~7位、8~15位、16~20位对应的输出选择信号分别是00、01、10,11为禁止状态。计数器的位长和控制信号还可以根据需要灵活设置。

3・2窗口电路的集成化设计

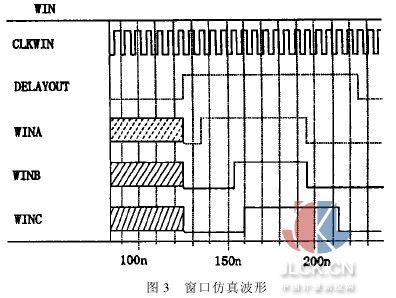

时钟窗口的设置限定了接收超声波信号的时间范围,是消除噪声影响的重要手段。传统的窗口电路一般由单稳态触发器实现,窗口的宽度由外接电阻和电容的值决定,调整起来很不方便,输出波形也不够理想。采用集成化设计后,窗口的起始位置和宽度都由使用同一个时钟的不同计数器的计数值来控制,精度大大提高。而且由于窗口是由数字电路产生的,所以波形也非常好。窗口电路的功能仿真波形如图3所示。其中CLKWIN是时钟信号,DELAYOUT是延时计数器的输出,用来限定窗口的范围,WINA、WINB、WINC是用于控制功能的3个窗口。

3・3触发器和逻辑器件的集成化设计

触发器和各种逻辑器件集成到ispLSI中相对比较容易。可以根据需要灵活地设置触发器的种类和形式,如是否有置位复位端,是同步还是异步等。逻辑功能的实现只要给出输入输出端口和它们之间的逻辑表达式就行了。

4结论

PLD器件的应用,使超声波流量计硬件电路设计中所用IC器件的数量明显减少。用两片ispLSI 1032实现了原设计中约30片IC的功能,不仅减小了设计电路板的面积,同时提高了系统的稳定性和设计灵活性。

摘自:中国计量测控网