基于FPGA的超声信号采集系统

发布时间:2017-09-01

1引言

传统的数据采集系统往往采用单片机或数字信号处理器作为控制器、控制模/数转换器、存储器和其他外围电路,但时钟频率较低,各种功能靠软件的运行来实现,效率较低,难以满足数据采集系统实时性和同步性的要求。然而基于DSP的数据采集系统,虽然处理速度快,但成本较高,过于频繁的中断会使CPU 的效率降低,响应速度变差。采用FPGA为核心设计的采集系统,时钟频率高,内部时延小,简化外围电路、降低设计风险、缩短开发周期,大大提高了系统的性能,将广泛用于高速数据采集系统中[1]。本文充分利用FPGA这方面优势,提出一种基于FPGA的高速超声信号采集系统,对来自超声传感器的高频信号进行放大、A/D转换和高速缓存等处理。

2基于FPGA采集系统的设计

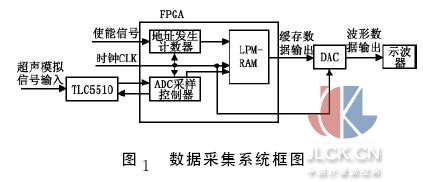

数据采集系统中的控制逻辑单元采用ALTERA公司的EP1C3T144芯片,内部的A/D采样控制器控制A/DC芯片采集超声检测模拟信号,将A/D转换好的8位数据送到FPGA 内部定制好的RAM 存储器中存储。ADC芯片采用美国德州仪器(TI)公司的TLC5510,转换速率最高可达到50MSPS,换电压量程为0.6V~2.6V。缓存选用单端口RAM 存储器,在" MegaWizardPlug-InManager" 内部定制,RAM 的数据宽度和ADC的输出数据宽度要一致,当RAM 存储器中完成一个至数个周期的被测信号采样后,在地址发生器的地址扫描下,将存于RAM 中的数据通过DAC的输出端进入示波器,完成对FPGA工作状态的实时观测和调试,从而可以准确地验证整个传输过程中数据的正确性和时序性是否满足设计需求。试验系统中模块所需的时钟由全局时钟CLK直接提供,使能信号由配置的试验箱上的按键Key1控制。系统结构框图如图1所示。

2.1ADC控制模块设计

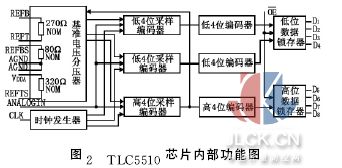

图2为TLC5510芯片内部功能图,CLK(时钟信号)、OE(输出使能信号)为TLC5510芯片控制信号,与ADC采样控制器的链接见图2所示。ADC采样控制器接收到FPGA 系统信号采集使能信号后,启动TLC5510采集原始数据,超声模拟信号从ANALOGIN 引脚单端输入,在转换时钟CLK 控制下转换为8位数字信号,当输出使能信号OE低电平有效时,转换后的数字信号D1~D8并行输出。本文接PIN_16引脚时,通过跳冒来选择20MHz有源晶振,并打开电源开关为A/D芯片提供电源。

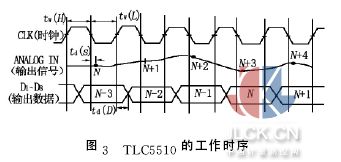

图3为TLC5510的采样时序图,TLC5510是以流水线的工作方式进行工作。当第一个时钟周期下降沿到来时,模拟输入电压将被采样到高比较器块和低比较器块,高比较器块在第二个时钟周期的上升沿的最后确定高位数据;同时,低基准电压产生与高位数据相应的电压。低比较块在第三个时钟周期的上升沿的最后确定低位数据。高位数据和低位数据在第四个时钟周期的上升沿进行组合。这样,采样转换结果的输出却在2.5个CLK周期后送到内部数据总线上。此时如果输出使能OE有效,转换后的8位数据就被存储到RAM 缓冲器中。

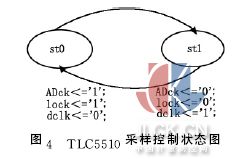

根据采样时序,用状态机来描述采样控制过程。图4所示为TLC5510采样控制状态图,在状态st0,给A/D一个采样时钟ADck的上升沿,同时锁存A/D的输出;在状态st1。给出采样控制模块数据输出锁存信号。A/D采样控制器的输出共有4个信号:ADck提供采样时钟;ADoe为TLC5510的输出使能,一直有效;data为采样数据输出;dclk用来同步data的输出,作为下一级的data锁存信号。

2.2RAM 控制模块设计

存储器是数据采集系统的重要组成部分,负责将采集后输出的数字信号进行存储,以等待下一步操作。QuartusⅡ中含有大量功能强大的LPM 模块,本文选用FPGA片内的LPM-RAM 宏模块来实现这种存储器,输入和输出可以支持不同的时钟或者同一个时钟来完成A/D转换输出的数字信号的缓存和输出。RAM 控制模块的连接见图1所示。

在QuartusⅡ7.2的" MegaWizardPlug-InManager" 设计与定制界面里定制的LPM-RAM模块,主要是参数的设置,如器件的选择、数据数量等。本文选择Cyclone器件,RAM 的数据线宽度8,地址线宽度10,数据数量1024,有一个地址锁存时钟和一个写使能控制线。在存储容量和采样速率一定的情况下,定制的RAM 存储器可检测的工件厚度最大为30cm(以钢件作为参考件),满足一般的管材、棒材和板材检测。与外挂的SDRAM 相比,内嵌的RAM 集成在FPGA内部,在逻辑设计上更简单明了,更容易控制和分析,便于进行精确的仿真和调试,充分利用FPGA的资源。

3试验结果

实验采用GW48试验箱,选用电路结构图NO.5,在QuartusⅡ7.2 开发平台上建立工程,用VHDL语言编辑数据采集和存储程序,分配管脚,编译成功后通过JTAG 下载线下载到试验箱上。使能信号由试验箱上的KEY1控制,在KEY1高电平时,每一个CLK 时钟信号的上升沿完成加一计数,指向下一个RAM 单元,ADC5510 采样进入RAM,并将采样的数据存入这个RAM 单元,完成高速数据的缓存。低电平禁止写入,允许扫描输出给5651,接示波器上显示出来,以观察存入到rom1中的数据信息是否与超声信号相似,评价该采样系统的性能。由于用到的D/A 芯片是超高速、10位分辨率的THS5651,所以将其低两位赋0。

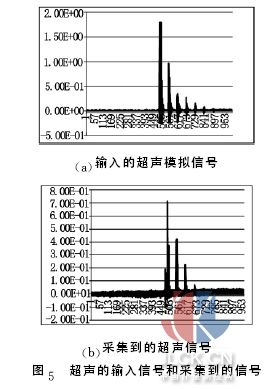

图5为采样前输入超声信号波形和采样后的超声信号波形图。通过对比采样前后的超声波形可以发现,输入超声信号能看到很多次底波,而采样后的信号只能看到二次底波和正的幅值。这是因为超声信号里含有很多噪声信号,采样过程中底波信号的电压比较小时会被噪声信号覆盖,而且示波器本身也有很多噪声信号,当输入的超声信号的电压很小时,也会把超声信号覆盖,且由A/D模块的输入电压范围决定系统只能采集0.6V~2.6V 之间的超声信号波形。但该数据采集系统实现了超声信号的高速采样和缓存过程,将超声信号转换为数字信号处理,可以提高对缺陷定位、定量的精度。

4结束语

基于FPGA 的超声信号采集系统实现了超声信号的超高速采集和存储,但还需要做好噪声信号处理方面的问题,如对信号进行滤波处理,防止超声信号被覆盖等。若存储数据量很大时,因FPGA内部存储资源有限,还需要扩展外部的存储资源,应注意时序的控制使传输速度之间协调。

摘自:中国计量测控网